Xilinxs interconnect is a general cross bar switch. The crossbar switch can switch inputs yellow color squares to the outputs cyan color squares - imagine each box is a CPU or a memory module.

Pdf Vhdl Implementation Of 4x4 Crossbar Switching

A simple simulation result.

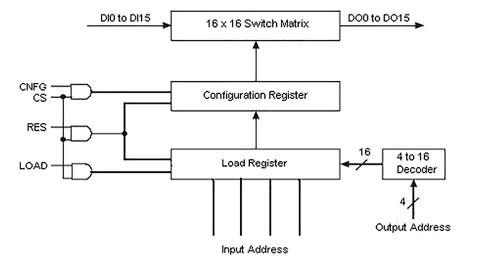

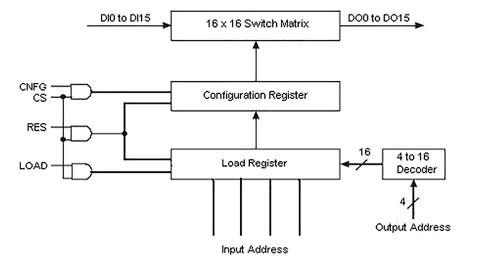

. BUILT IN - ARTICLE INTRO SECOND COMPONENT. A 16x16 crosspoint switch is a non-blocking crosspoint switch which allows you to independently connect each output to any input and any input to any output. The presented crossbar requires a two-dimensional arbitration that incorporates a diagonally rotated priority to provide fair arbitration.

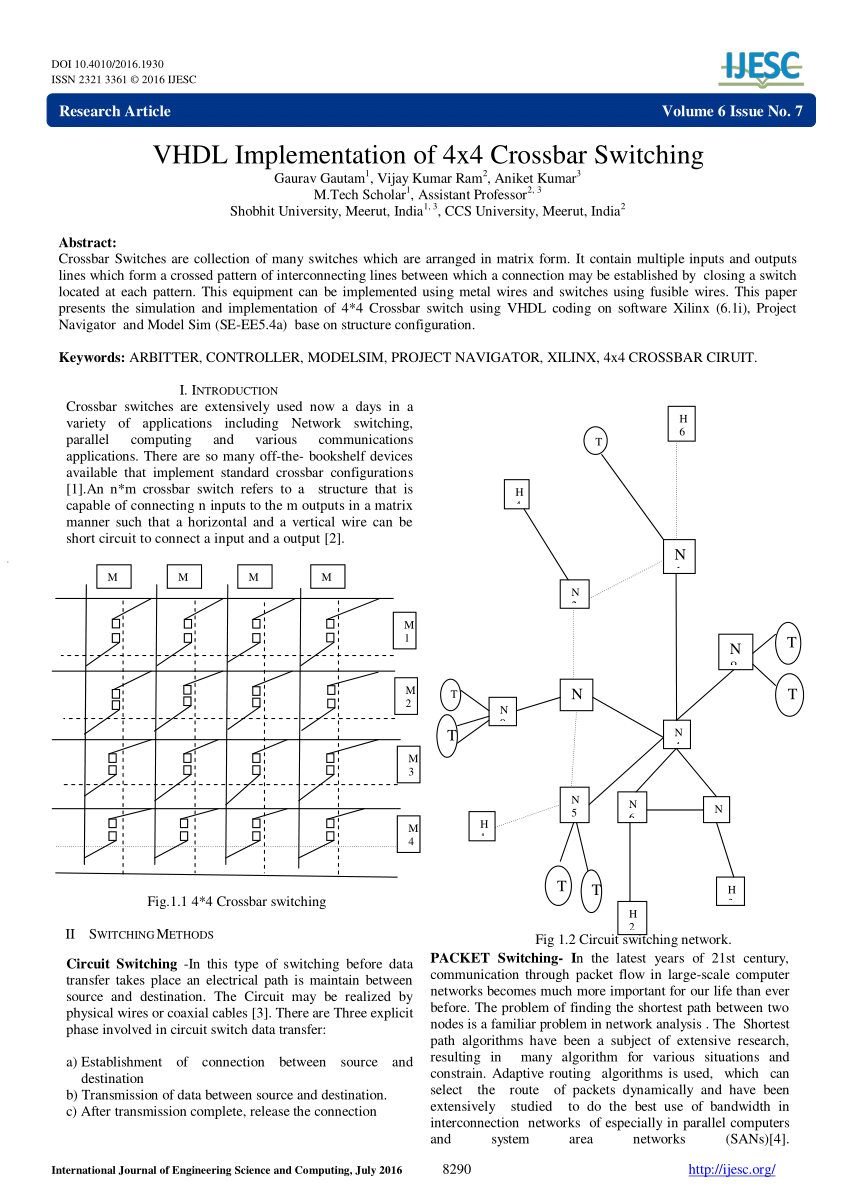

The arbiter is capable of performing arbitration in 1ns on Vertex 6 FPGA technology for an 8 x 8 crossbar. Connected crossbar - any pin can be sourced from any other pin. A crossbar switch has multiple input and output lines that form a crossed pattern of interconnecting lines between which a connection may be established by closing a switch located at each intersection the elements of the matrix.

In addition to the circuit design to incorporate. Switch matrix configuration and address decoder. You can connect each port to any other port as an output or input.

Crossbar Switch in Verilog HDL Ben A. This project aims at designing a data packet routing system to tackle communication between different modules in a common bus specifically use VHDL code to implement circuit diagram as following. Shankar Narayanan Neelakrishnan Keywords.

The work presents Verilog implementation modeling and synthesis of 8-bit 4 4 crossbar switch for virtual channel router. Each port is 8 bits wide and can be in tri-state mode making it an input port. It uses an 8-bit wide control input.

¾Energize horizontal bar A ¾Energize free vertical bar P ¾De-energize horizontal bar A ¾Energize horizontal bar B. It instantiates a single. I am looking for a crossbar switch core processor design in verilog HDL.

Originally a crossbar switch. The 16x16 crosspoint switch is divided into three major sections. Crossbar Switch Quantum Dot Cellular Automata System Verilog Schedulers for DCX Introduction The increasing demand of fast and compact System on Chip SoC has led to development of high density and low power circuits to be integrated on a single chip.

More see in Simulation_Results. The sources inputs first send request signals to the switching logic circuit. This design implements a 4-port crosspoint switch where all four ports are bidirectional.

Design and implementation of NoC routers and their application to Prdt-based NoCs Author. Each switch point has control logic to set up the transfer path among a memory and processor. Then fill them in with a glitter polish.

Blocking crossbar switches Scheme 1 2NK switches ¾N denotes the number of subscribers ¾K is the number of simultaneous connections Operate four bars to establish a connection eg. The code shown here has been simulated and verified using Bluesim. That you write 128 times to set all of the pins this would not be good the way its coded because theres.

Would you please point me to. This document describes the design of a highly parameterized recursively defined crossbar switch written in Bluespec SystemVerilogTM BSV. 5x5 with input or output buffering.

HiI need a verilog code for a banyan switch. In each crosspoint the small square represents a switch which obtains the path from a processor to a memory module. Parameter DATA_WIDTH 32 Width of address bus in bits.

Thanks a lot Ben ----- next part ----- An HTML attachment was scrubbed. The design of the crossbar fabric is shown in Figure 1In other words the crossbar-based fabric switch is the dominant architecture for todays high-performance packet switches 12 13. Abderazek 2006-12-21 104054 UTC.

In fact the resistor just is the turn-on and turn-off resistance of the switch. Do not forget to incorporate a leading coat to seal every little thing in. In electronics and telecommunications a crossbar switch is a collection of switches arranged in a matrix configuration.

PDF On Jan 30 2015 Sajad Ahmad Ganiee and others published FPGA Design of 8 bit 44 Crossbar Switch for Multi Processor System on Chip Using Round Robin Arbitration Algorithm Find read and. The crossbar components are widely used in router and switches. The reference design includes the verilog source design files for the three sections.

This high performance crossbar is coined with Diagonal Propagation Arbiter DPA. As in Verilog it is a module constructor ie it can be instantiated more than once. It does a completely.

Then fill them in with a glitter polish. Here Ive attached a simple Verilog crossbar design to estimate slice usage. This paper presents the simulation and implementation of 44 Crossbar switch using VHDL coding on software Xilinx 61i Project.

If there are two inputs say x1 and x2 and two outputs say y1 and y2 there is a select line s for s0 i must send the data through upper port for s1 i must send data through lower port. Mainly crossbar is used as an interconnection network in NoC. I am looking for a crossbar switch core processor design in verilog HDL.

A crossbar switch may serve as switching fabric to provide a non blocking network configuration. Verilog 2001 resetall timescale 1ns 1ps default_nettype none AXI4 crossbar module axi_crossbar Number of AXI inputs slave interfaces parameter S_COUNT 4 Number of AXI outputs master interfaces parameter M_COUNT 4 Width of data bus in bits. The setting of the switching fabric is under the control of a switching logic circuit.

Maybe you can create a voltage controlled resistor as a switch when switch-on set the resistance 0 when switch-off set the resistance a large number see 1e15. Crossbar Switch system contains of a number of crosspoints that are kept at intersections among memory module and processor buses paths. Crossbar switch design in verilog Just grab a nail polish pen and attract minimal imperfect semi-circles.

The fabric of a crossbar-based packet switch can be either unbuffered 12 or internally buffered 13. It connects one or more AXI memory-mapped master devices to one or more memory-mapped slave devices In general a crossbar switch allows any number of bus masters to access any number of bus slaves with the general rule that only one master can talk to any given slave at a time. 5 ports with inputs or outputs buffering Would you please point me to some work or source code link.

Customized 4-Port Crosspoint Switch.

Pdf Vhdl Implementation Of 4x4 Crossbar Switching

Verilog Hdl 16x16 Crosspoint Switch Design Example Intel

Figure 3 From Fpga Design Of 8 Bit 4 4 Crossbar Switch Formulti Processor System On Chip Using Roundrobin Arbitration Algorithm Semantic Scholar

Vhdl Code For The 2 2 Crossbar Switch Example Download Scientific Diagram

Design And Implementation Of Crossbar Scheduler For System On Chip Network In Quantum Dot Cellular Automata Technology Thakur 2018 Internet Technology Letters Wiley Online Library

Multicasting Crossbar Switch Architecture Download Scientific Diagram

Pdf Fpga Design Of 8 Bit 4 4 Crossbar Switch For Multi Processor System On Chip Using Round Robin Arbitration Algorithm

0 comments

Post a Comment